DDC-8DSP

|

Overview:

|

The eight-channel digital pulse

processors DDC-8DSP designed by Wojtek Skulski is yet another substantial upgrade.

Since the 500k gate FPGA on DDC-8LUX was utilized up to ~97% (VHDL code was

optimized) it was time to make the step towards an FPGA with a BGA

footprint which offers much more resources for incorporating

growing demands. The chosen Xilinx Spartan DSP FPGA yields a seven (7)

fold increase in overall resources. Besides obvious

advantages like number of gates (3400k) and memory (283kB), one of the

very promising upgrades is the 126 multiply-accumulate blocks

which further extend the on-FPGA digital signal processing

possibilities. The ability of the board to use 14bit ADCs sampling at

125MHz makes the board a likely candidate for a DAQ board.

The

DDC-8DSP board has the capability of running on an external clock, which

makes it useful in applications where overall

time synchronization is critical. Additionally the clock distribution

chain on the board was redesigned to bring down the clock jitter below

10ps making the board attractive for timing applications.

|

---------------------------------------------------------------------------------------------------------------------------------------

|

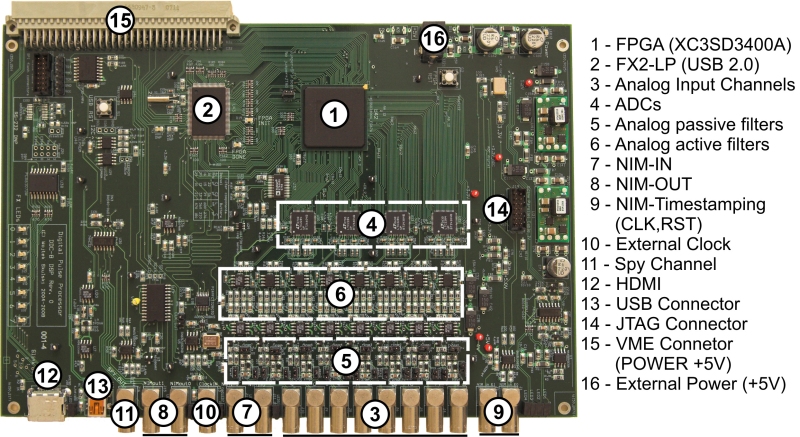

The board:

|

|

|

|

Main parameters:

|

|

DDC-8DSP |

| FPGA |

XC3SD3400A |

| Analog to Digital Converter |

14bit@up

to 125MHz |

| Number of channels |

8 |

| Block Memory |

283kB

(six times more than DDC-8LUX) |

| Buffer length per channel |

potentially

~6100 samples (+ zero suppression can be implemented) |

| Additional features |

126

Multiply-accumulate blocks

HDMI

high speed connector

Timestamping NIMs (CLK,RST) |

|

Potential new firmware features:

|

- Digital channel sum

- Digital gain matching between the channels

- Pulse width measurements in real time

- DAQ capabilities

|

| --------------------------------------------------------------------------------------------------------------------------------------- |

Real application:

|

LUX Trigger

|

Eryk

Druszkiewicz, Frank Wolfs

|

| The

firmware from DDC-8LUX is being ported onto the new BGA FPGA with

additional new features. |

|

|