DDC-8

|

Overview:

|

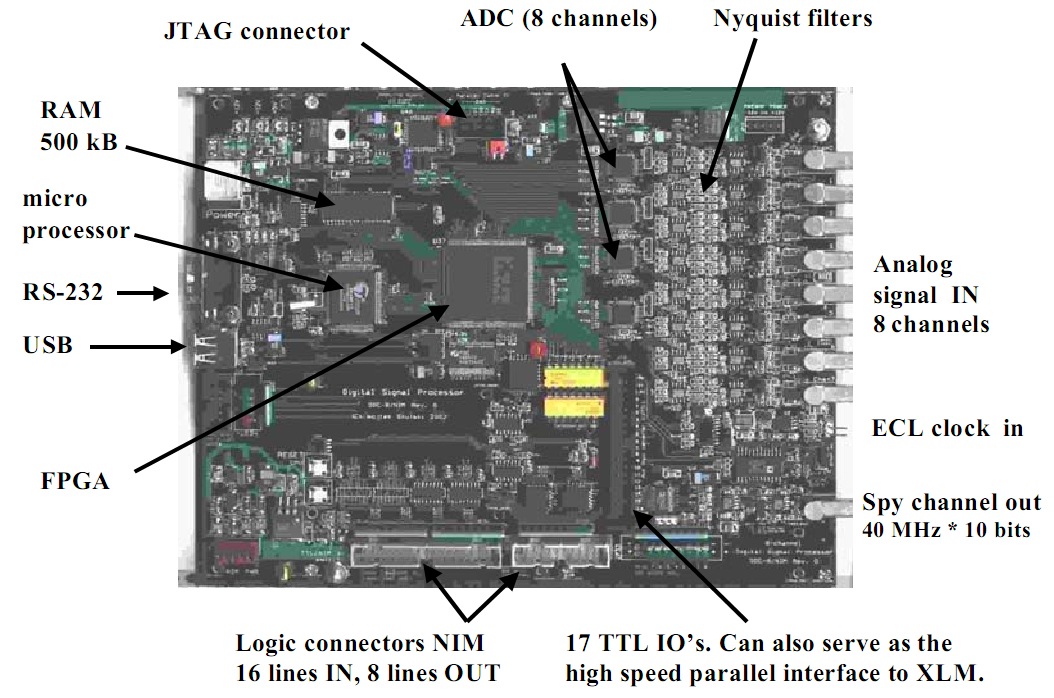

The eight-channel digital pulse

processor DDC-8 was originally intended to serve as a real-time trigger

for the PHOBOS experiment located in Brookhaven National Laboratory.

Besides this initial application, the device is targeted at flexible

general-purpose real-time digital pulse processing. The board features

eight analog input channels, as well as a large number of logic inputs

and outputs. The sixteen NIM inputs as well as seventeen TTL I/Os are

connected to the on-board FPGA in order to process coincidence signals

in real-time. The TTL lines can also serve as the high-speed,

bidirectional interface to the VME digital processor XLM-80. The USB

interface provides control of the device and medium-speed data readout,

while the RS-232 interface allows remote operation. The digital signal

processing is performed by the FPGA. The on-board microcontroller

performs the monitoring and communication chores. The photograph shows

the proctology board. The mechanical standard of the board is NIM. The

board can also be mounted in a CAMAC enclosure, or any other enclosure

from which it will receive +/-6V power.

|

---------------------------------------------------------------------------------------------------------------------------------------

|

The board:

|

|

|

|

Main parameters:

|

| FPGA |

Xilinx XC2S300E |

| Analog to Digital

Converter |

10bit@40MHz |

| Number of channels |

8 |

| Buffer

length per channel |

1024 samples |

|

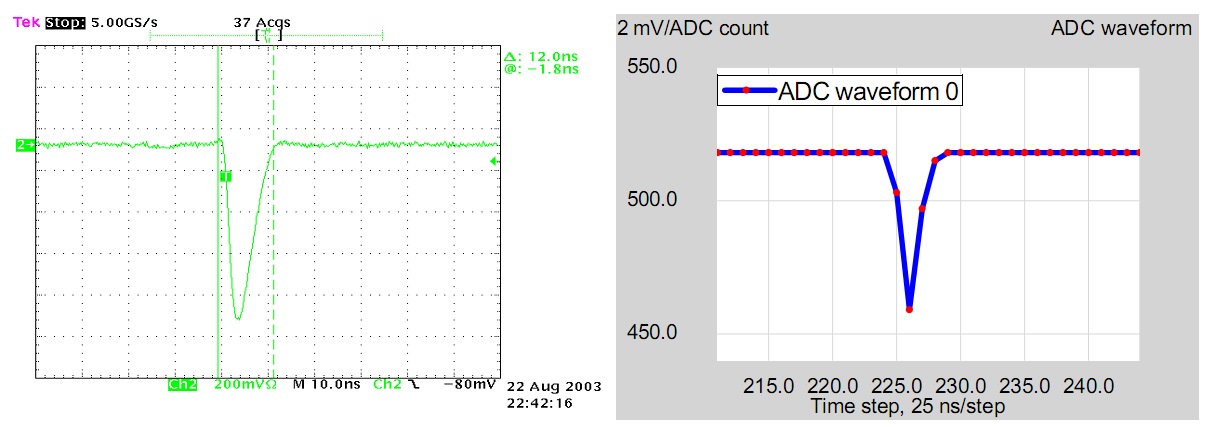

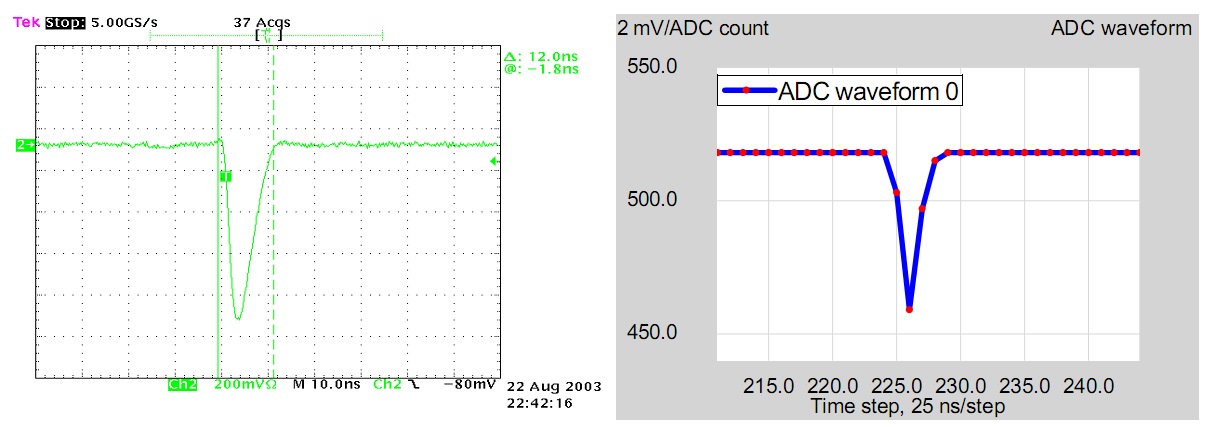

Sample digitized pulse:

|

Left:

A fast test pulse from the NIM pulser, which is a good approximation of

a pulse from a fast phototube. The pulse lasts for only half of the

DDC-8 sampling period. Right :

the waveform captured with DDC-8. |

| --------------------------------------------------------------------------------------------------------------------------------------- |

Real application:

|

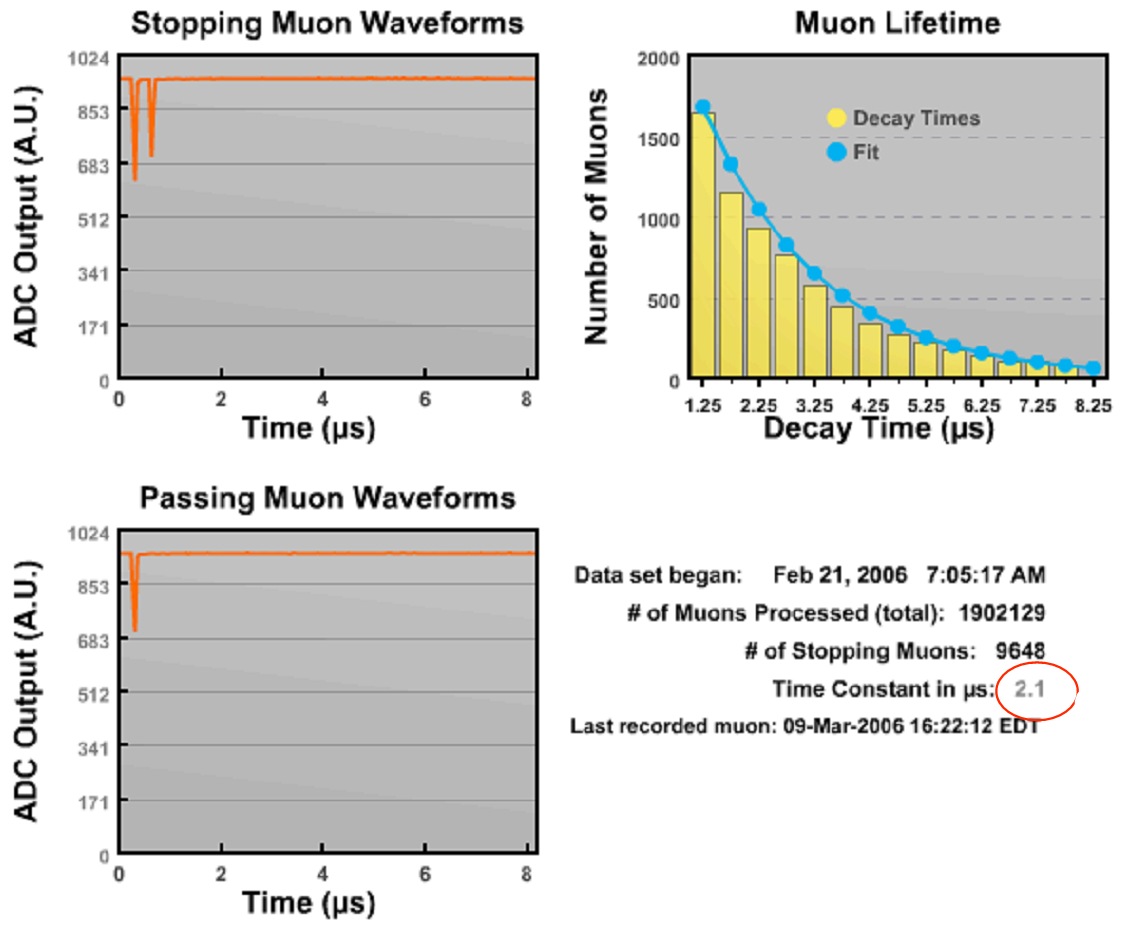

Online Muon Capture and Decay Experiment

|

Megan

Alexander, Daniel Miner,

Wojtek Skulski, Frank Wolfs

On-line Muon experiment is here

Presentation available here |

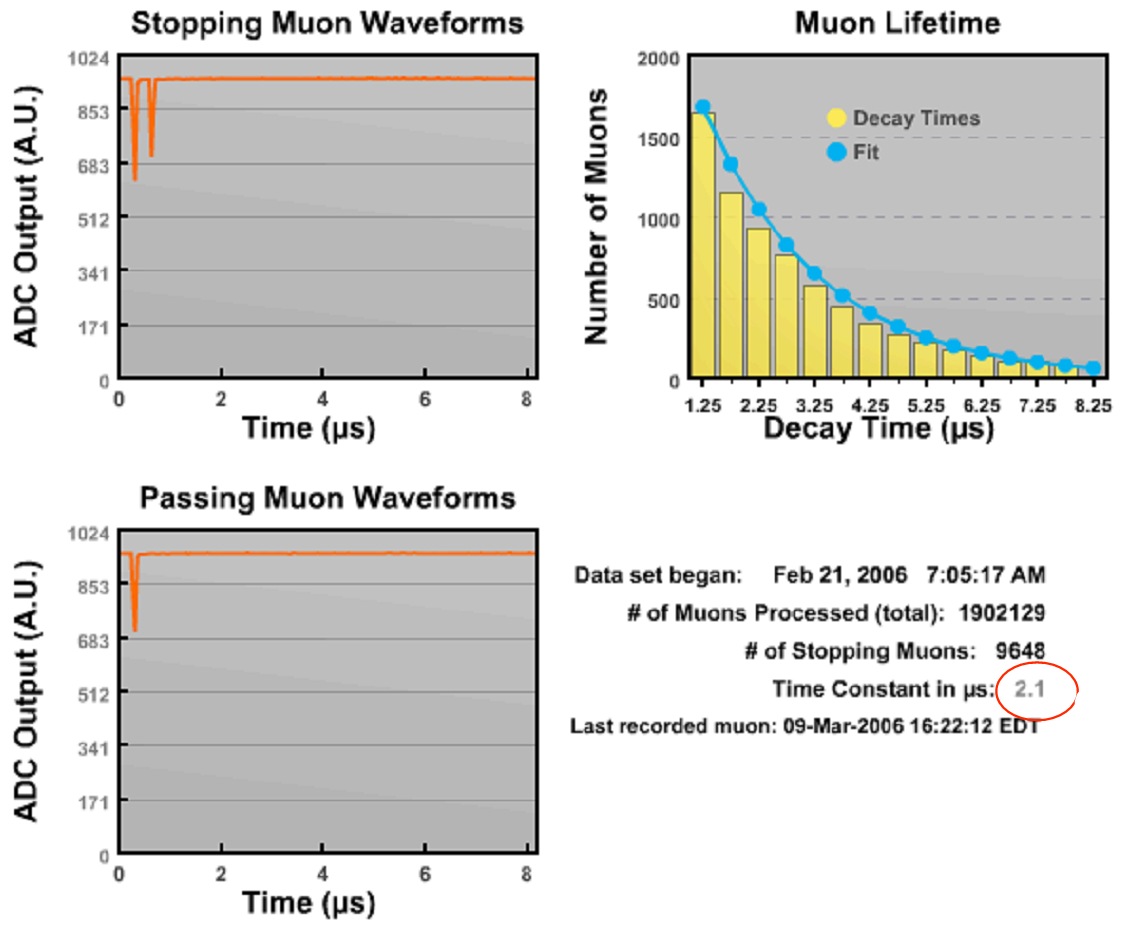

Sample screenshot of the on-line

muon experiment

|

|

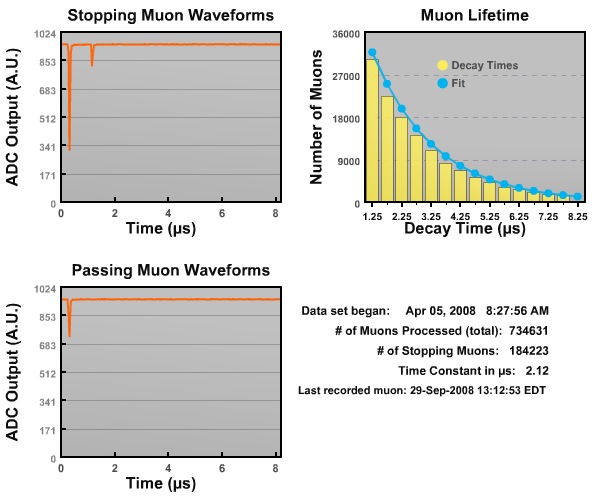

Implementing in FPGA stopping Muon detection for the

Online Muon Experiment

|

DDC-8

firmware enhancement by Eryk Druszkiewicz as a summer Research

Experience for Undergraduates (REU)

The goal was to add the ability to distinguish stopping from

passing muons on-the-fly using the FPGA on DDC-8. This then gave the

ability to control the ratio of passing to stopping muons

captured. As one can see in the screenshot above the uncontrolled ratio

is about ~200. Since the new firmware we were able to effectively

decrease the ratio. For example in the experiment summarized in the

figure below, the ratio was set to 4.

|

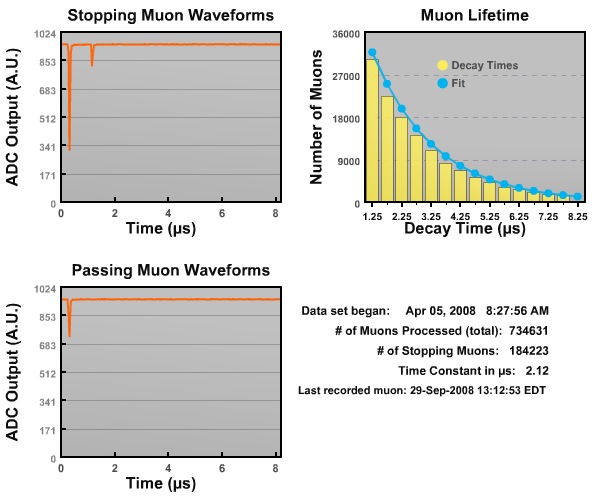

Sample screenshot of the on-line Muon Experiment with

on-the-fly muon detection

|

|

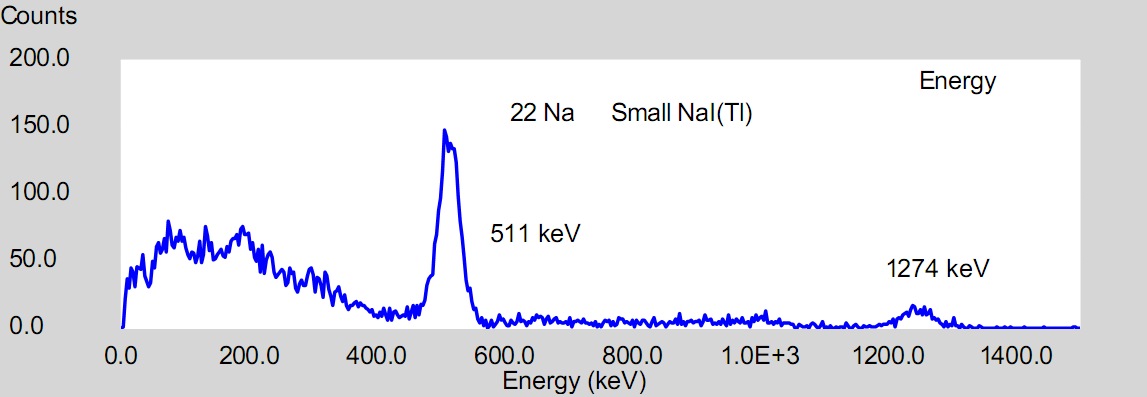

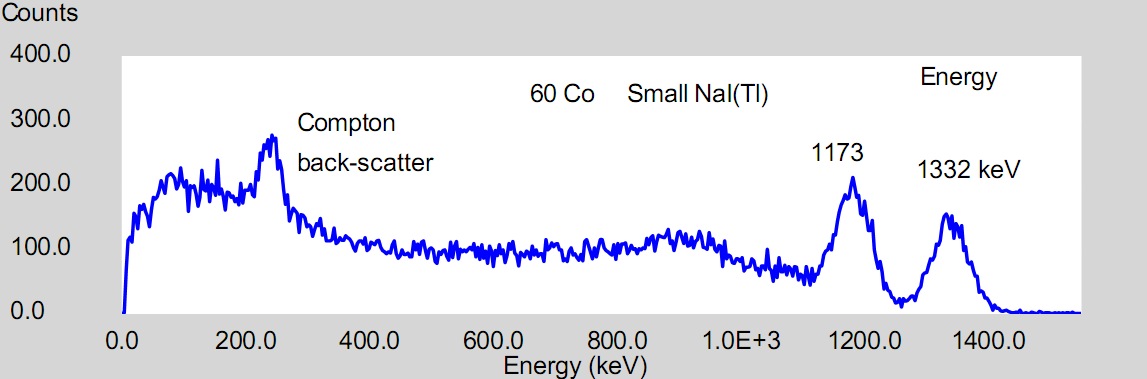

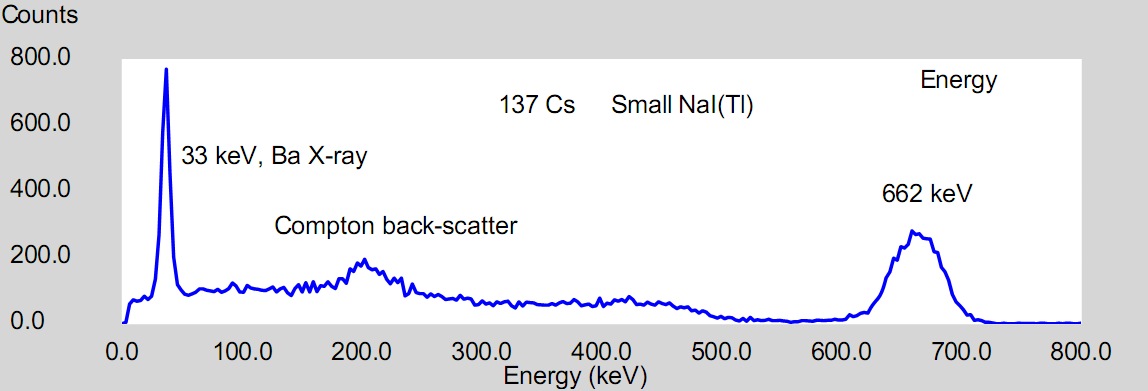

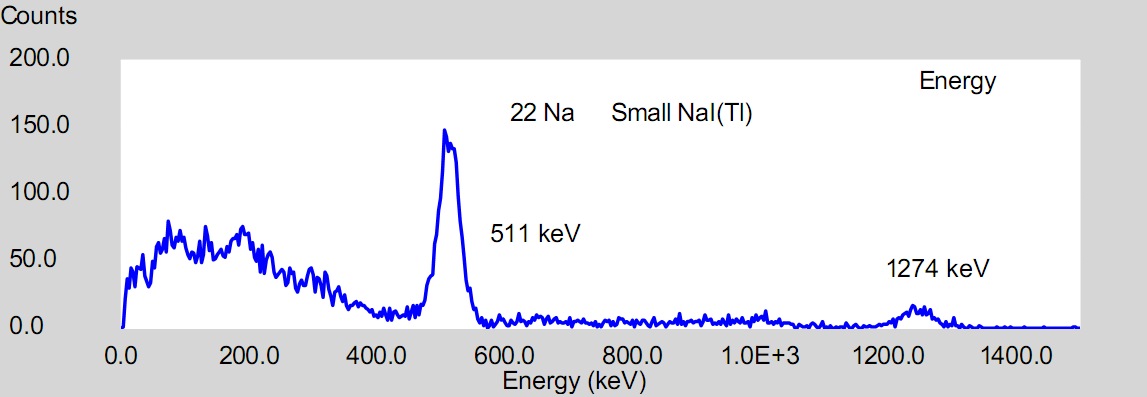

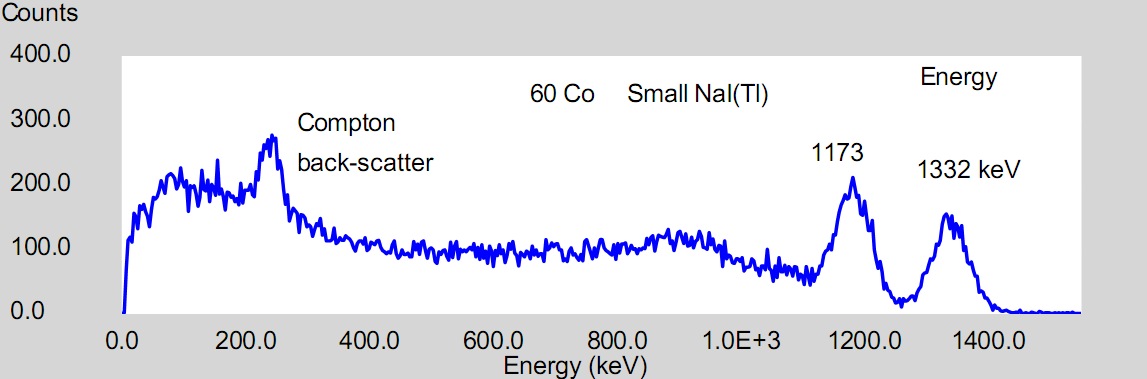

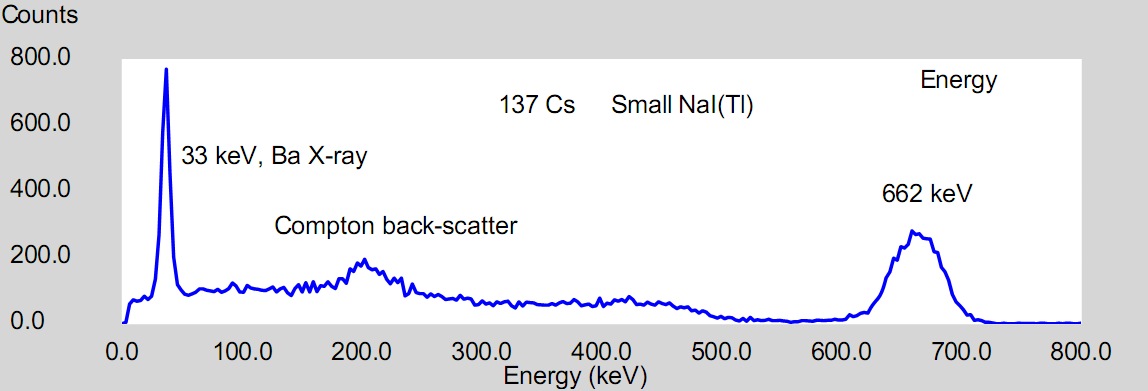

Energy spectra collection with the NaI(Tl) detector |

| Using

a DDC-8 board an energy threshold of as low as 5 keV was achieved with

the DDC-8 board during a measurement that extended into an MeV range. |

Sample 22 Na spectrum obtained with DDC-8

Sample Co60 spectrum obtained with DDC-8

Sample Cs spectrum obtained with DDC-8 |

|