DDC-1

|

Overview:

|

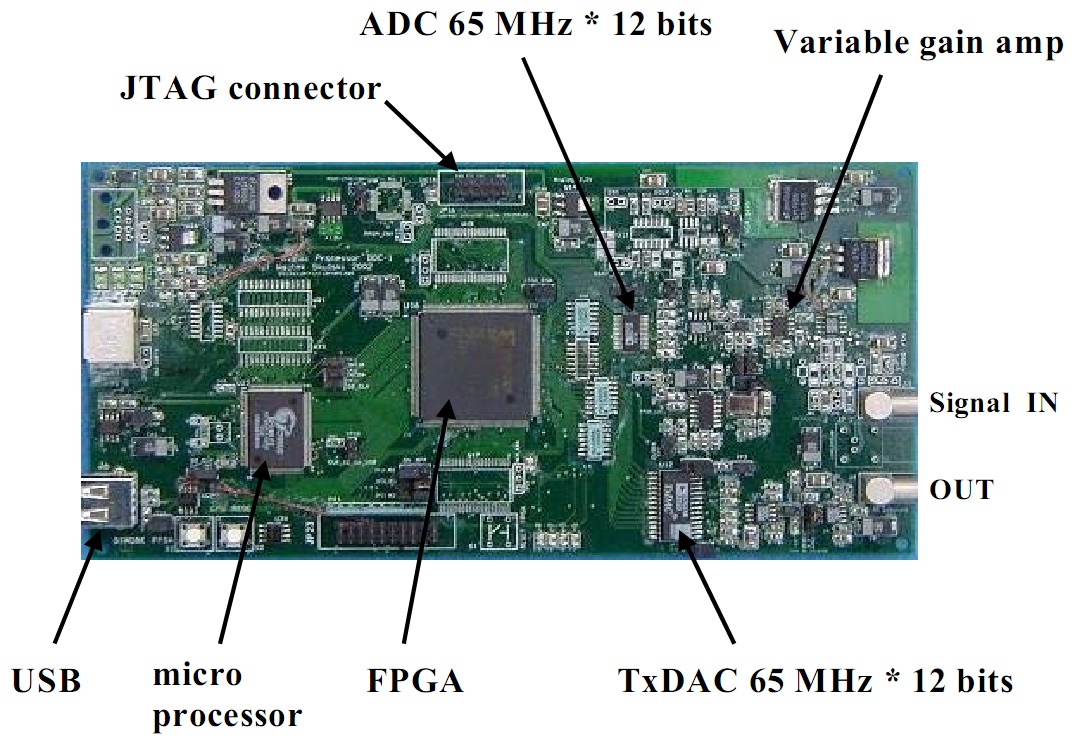

| A

single-channel digital pulse processor. The printed circuit board is

realized in the four-layer, surface-mount technology, with the

dedicated ground and power layers inside the board. The board is divided

into separate analog and digital parts. The analog front end consists

of an input buffer followed by variable-gain amplifier, followed by an

animalizing filter. In principle, both the gain and offset can be

controlled by the microprocessor. However, the DAC that is needed for

this purpose has not been soldered on the prototype board. The board

contains the 12-bit sampling ADC (middle part) and the 12-bit

reconstruction (lower part), both capable of up to 65 MHz sampling

rate. During the tests the device was operated at 48 MHz sampling rate.

The central part of the board is devoted to a field programmable gate

array (FPGA)and a microprocessor. The data can be directed both to the

USB connector and to the reconstruction TxDAC. The reconstructed analog

waveform is delivered to the output connector to be examined with an

oscilloscope in real time. |

---------------------------------------------------------------------------------------------------------------------------------------

|

The board:

|

|

|

|

Main parameters:

|

| FPGA |

Xilinx XC2S300E |

| Analog to Digital

Converter |

12bit@48MHz |

| Number of channels |

1 |

| Buffer

length |

1024 samples |

|

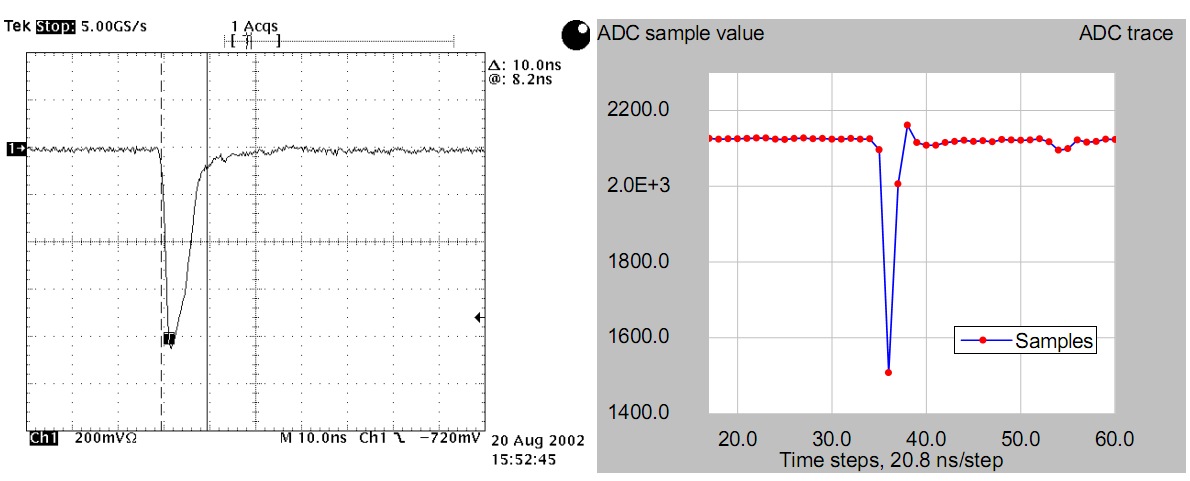

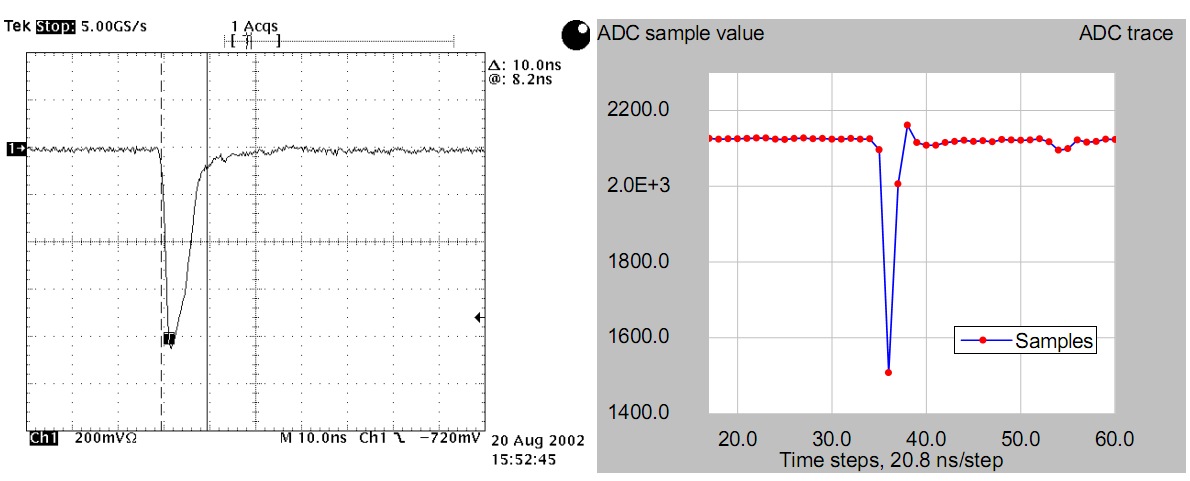

Sample digitized pulse:

|

Left:

A fast test pulse from the NIM pulser, which is a good approximation of

a pulse from a fast phototube. The pulse lasts for only half of the

DDC-1 sampling period. Right : the waveform captured with DDC-1. |

| --------------------------------------------------------------------------------------------------------------------------------------- |

Real application:

|

Digital Signal Processing of Scintillator Pulses in

Nuclear Physics Techniques

|

Senior

thesis by Saba Zuberi

Available here |

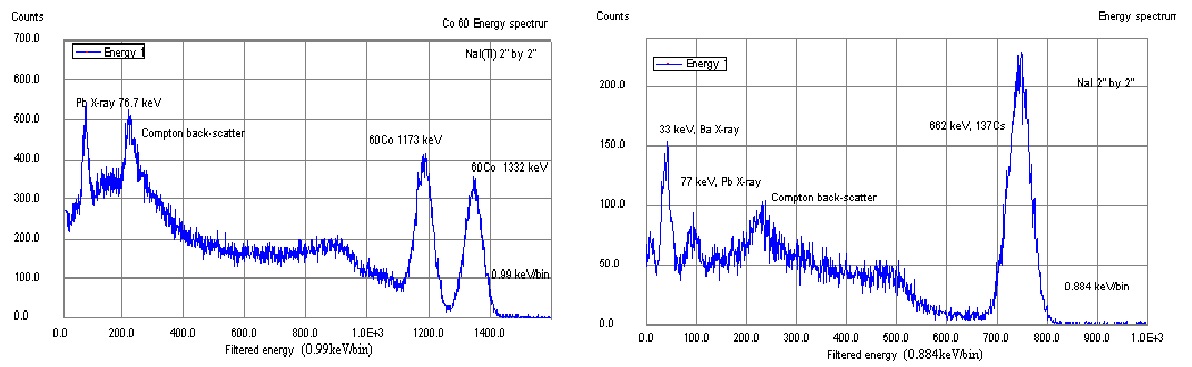

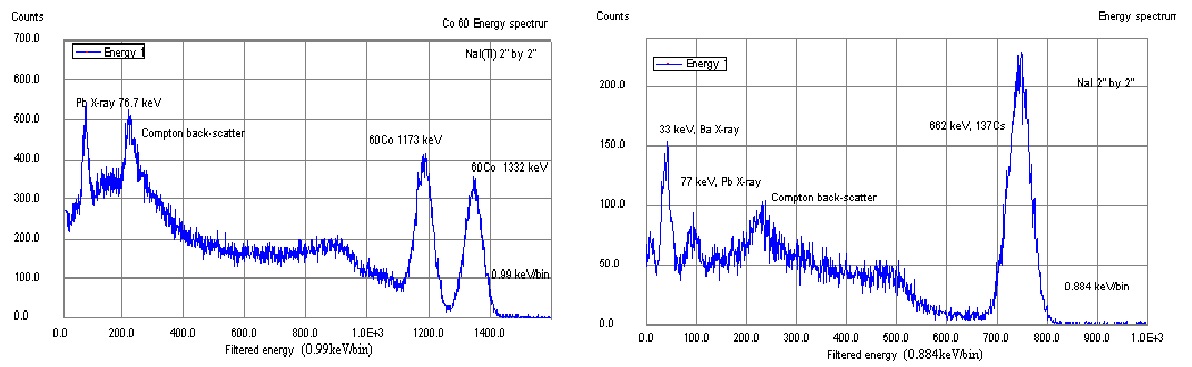

Sample energy spectra collected with NaI(Tl) detector and DDC-1 Left: Co60 Right: Cs137

|

|

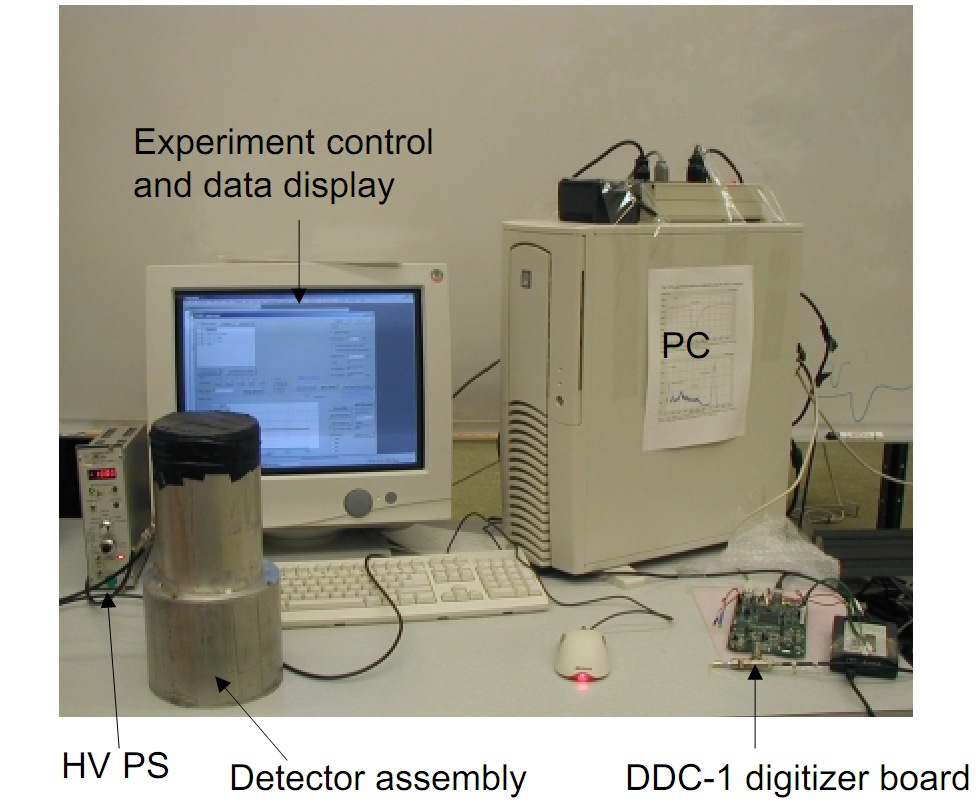

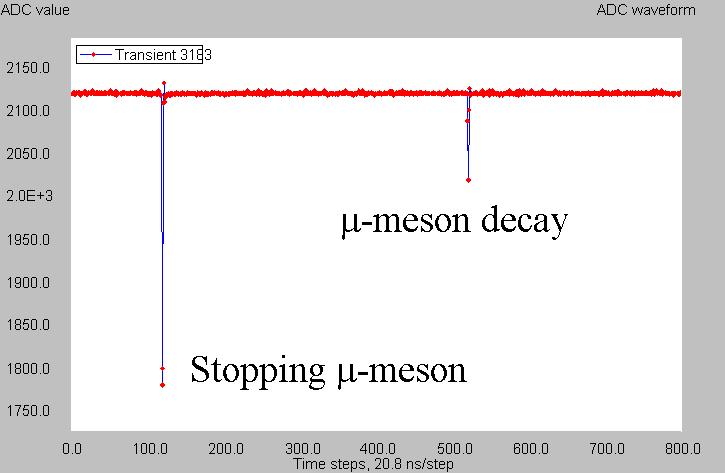

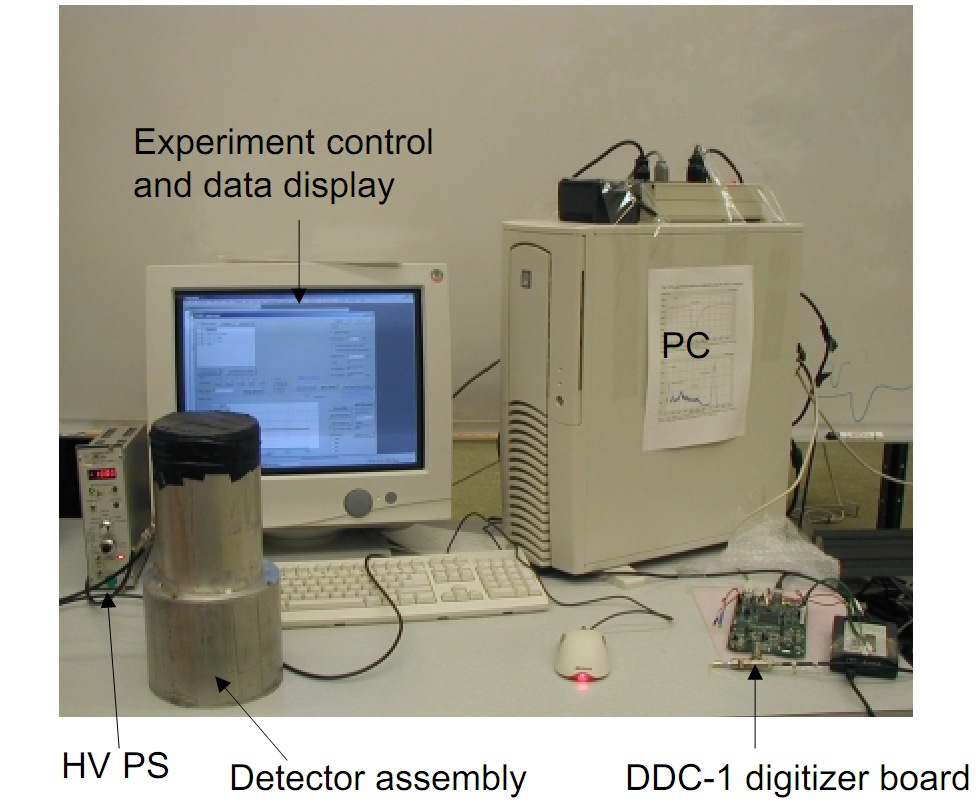

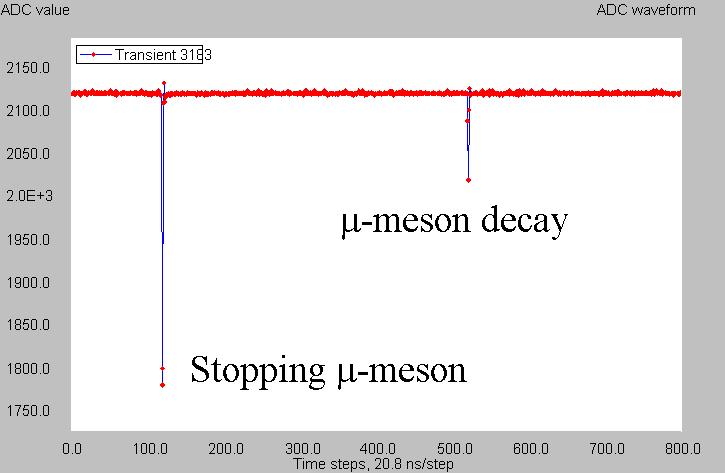

Detection and Analysis of Stopping Muons Using a

Compact Digital Pulse Processor

|

An

investigation was by Daniel Miner during his summer Research

Experience for Undergraduates (REU)

Report available here

Presentation available here |

The experiment setup

Sample muon event captured with DDC-1 |